# **Design of the 11011 Sequence Detector**

A sequence detector accepts as input a string of bits: either 0 or 1.

Its output goes to 1 when a target sequence has been detected.

There are two basic types: **overlap** and **non-overlap**.

In an sequence detector that allows overlap, the final bits of one sequence can be the start of another sequence.

| 11011 detector with overlap    | Х | 11011011011                |

|--------------------------------|---|----------------------------|

|                                | Ζ | 0000100 <mark>1</mark> 001 |

| 11011 detector with no overlap | Ζ | 00001000001                |

**Problem:** Design a 11011 sequence detector using JK flip-flops. Allow overlap.

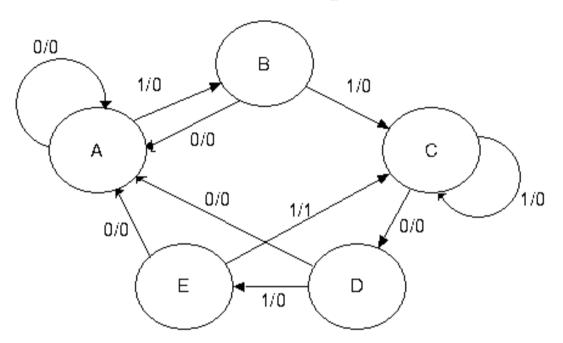

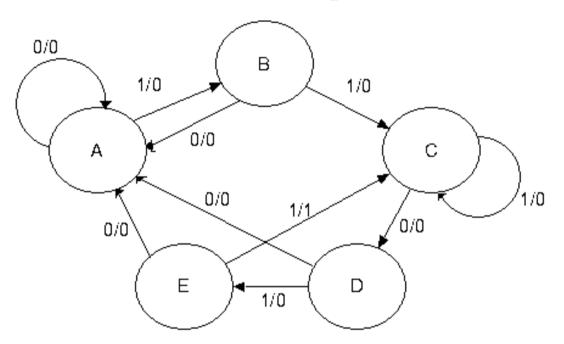

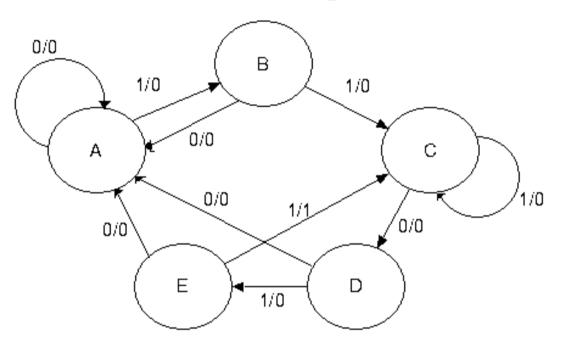

#### **Step 1 – Derive the State Diagram and State Table for the Problem**

### Step 1a – <u>Determine the Number of States</u>

We are designing a sequence detector for a 5-bit sequence, so we need 5 states. We label these states A, B, C, D, and E. State A is the initial state.

Step 1b - Characterize Each State by What has been Input and What is Expected

| State | Has  | Awaiting |

|-------|------|----------|

| А     |      | 11011    |

| В     | 1    | 1011     |

| С     | 11   | 011      |

| D     | 110  | 11       |

| E     | 1101 | 1        |

#### Step 1c – <u>Do the Transitions for the Expected Sequence</u>

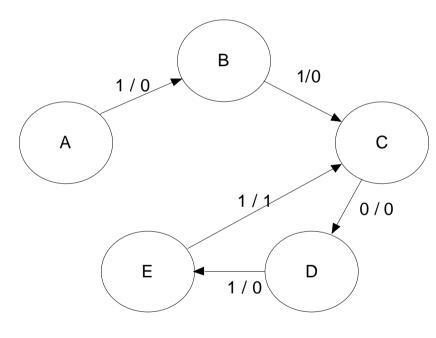

Here is a partial drawing of the state diagram. It has only the sequence expected. Note that the diagram returns to state C after a successful detection; the final 11 are used again.

Note the labeling of the transitions: X / Z. Thus the expected transition from A to B has an input of 1 and an output of 0.

The transition from E to C has an output of 1 denoting that the desired sequence has been detected.

# The sequence is $1 \ 1 \ 0 \ 1 \ 1$ .

# Step 1d – <u>Insert the Inputs That Break the Sequence</u> The sequence is 1 1 0 1 1.

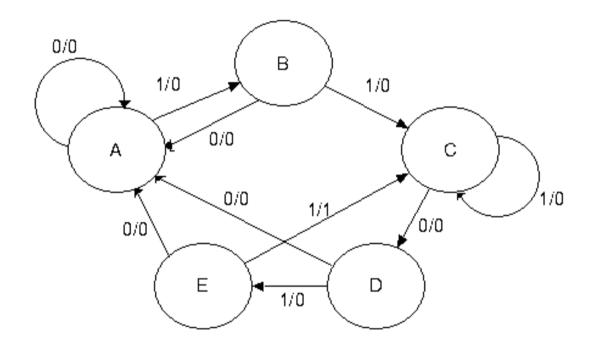

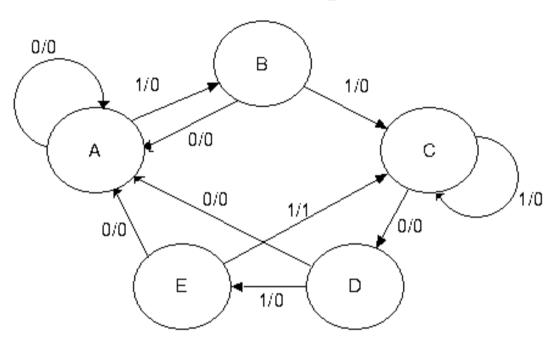

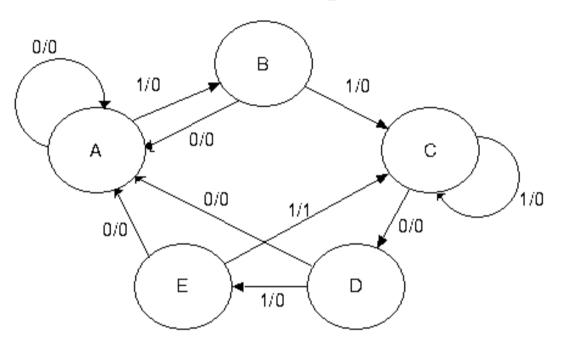

Each state has two lines out of it – one line for a 1 and another line for a 0. The notes below explain how to handle the bits that break the sequence.

### **State A in the 11011 Sequence Detector**

**A** State A is the initial state. It is waiting on a 1.

If it gets a 0, the machine remains in state A and continues to remain there while 0's are input.

If it gets a 1, the machine moves to state B, but with output 0.

### **State B in the 11011 Sequence Detector**

**B** If state B gets a 0, the last two bits input were "10".

This does not begin the sequence, so the machine goes back to state A and waits on the next 1.

If state B gets a 1, the last two bits input were "11". Go to state C.

### **State C in the 11011 Sequence Detector**

C If state C gets a 1, the last three bits input were "111".It can use the last two to be the first two 1's of the sequence 11011, so the machine stays in state C awaiting a 0.

If state C gets a 0, the last three bits input were "110". Move to state D.

### **State D in the 11011 Sequence Detector**

**D** If state D gets a 0, the last four bits input were "1100". These 4 bits are not part of the sequence, so we start over.

If state D gets a 1, the last four bits input were "1101". Go to state E.

### **State E in the 11011 Sequence Detector**

**E** If state E gets a 0, the last five bits input were "11010". These five bits are not part of the sequence, so start over.

If state E gets a 1, the last five bits input were "11011", the target sequence. If overlap is allowed, go to state C and reuse the last two "11". If overlap is not allowed, go to state A, and start over.

# **Prefixes and Suffixes: State C**

When breaking the input, we look for the largest suffix of the actual input that is an equal-length prefix of the desired pattern.

**State C**, with the last input = 1.

The last three bits input were "111".

|       | Input<br>"111" | Desired Sequence<br>"11011" | ce.        |                   |               |

|-------|----------------|-----------------------------|------------|-------------------|---------------|

| 1 bit | "1"            | <b>``1''</b>                | Good match | 11 <mark>1</mark> | <b>1</b> 1011 |

| 2 bit | "11"           | "11"                        | Good match | 1 <b>11</b>       | <b>11</b> 011 |

| 3 bit | "111"          | "110"                       | No match.  | 111               | <b>110</b> 11 |

The last two 1's at this state can form a 2-bit prefix useable at state C.

Chapter 7 Appendix

# **Prefixes and Suffixes: State E**

**State E**, with last input = 0.

The last five bits were "11010". No suffix of this is a prefix of the target.

|       | Input<br>"11010" | Desired Sequence.<br>"11011" |           |

|-------|------------------|------------------------------|-----------|

| 1 bit | "0"              | <b>``1`</b> '                | No match. |

| 2 bit | "10"             | "11"                         | No match. |

| 3 bit | "010"            | "110"                        | No match. |

| 4 bit | "1010"           | "1101"                       | No match. |

| 5 bit | "11010"          | "11011"                      | No match. |

| <b>Step 1e –</b> | Generate | the State | <b>Table with</b> | Output |

|------------------|----------|-----------|-------------------|--------|

|------------------|----------|-----------|-------------------|--------|

| Present State | Next State / Output |              |  |  |  |

|---------------|---------------------|--------------|--|--|--|

|               | $\mathbf{X} = 0$    | <b>X</b> = 1 |  |  |  |

| A             | A / 0               | B / 0        |  |  |  |

| В             | A / 0               | C / 0        |  |  |  |

| С             | D / 0               | C / 0        |  |  |  |

| D             | A / 0               | E / 0        |  |  |  |

| E             | A / 0               | C / <b>1</b> |  |  |  |

Step 2 – <u>Determine the Number of Flip-Flops Required</u>

We have 5 states, so N = 5. We solve the equation  $2^{P-1} < 5 \le 2^{P}$  by inspection, noting that it is solved by P = 3. So we need three flip-flops.

Step 3 – <u>Assign a unique P-bit binary number (state vector) to each state</u>.

The simplest way is to make the following assignments

A = 000 B = 001 C = 010 D = 011E = 100

Here is a more interesting assignment.

States A and D are given even numbers. States B, C, and E are given odd numbers. The assignment is as follows.

| A = 000 |                                        |

|---------|----------------------------------------|

| B = 001 |                                        |

| C = 011 | States 010, 110, and 111 are not used. |

| D = 100 |                                        |

| E = 101 |                                        |

### Step 4 – <u>Generate the Transition Table With Output</u>

| Prese | ent State                                    | Next Sta            | te / Output                                      |

|-------|----------------------------------------------|---------------------|--------------------------------------------------|

|       |                                              | <b>X</b> = <b>0</b> | X = 1                                            |

|       | $\mathbf{Y}_{2}\mathbf{Y}_{1}\mathbf{Y}_{0}$ | $Y_2Y_1Y_0$ / Z     | Y <sub>2</sub> Y <sub>1</sub> Y <sub>0</sub> / Z |

| Α     | 0 0 0                                        | 0 0 0 / 0           | 0 0 1 / 0                                        |

| В     | 001                                          | 0 0 0 / 0           | 0 1 1 / 0                                        |

| С     | 0 1 1                                        | 1 0 0 / 0           | 0 1 1 / 0                                        |

| D     | 100                                          | 0 0 0 / 0           | 1 0 1 / 0                                        |

| E     | 101                                          | 0 0 0 / 0           | 011/1                                            |

Note that bit 0 can clearly be represented by a D flip–flop with  $D_0 = X$ .

#### Step 4a – <u>Generate the Output Table and Equation</u>

The output table is generated by copying from the table just completed.

|                | ese<br>ate     | ent            | X =<br>0 | X =<br>1 |

|----------------|----------------|----------------|----------|----------|

| Y <sub>2</sub> | Y <sub>1</sub> | Y <sub>0</sub> | 0        | 0        |

| 0              | 0              | 0              | 0        | 0        |

| 0              | 0              | 1              | 0        | 0        |

| 0              | 1              | 1              | 0        | 0        |

| 1              | 0              | 0              | 0        | 0        |

| 1              | 0              | 1              | 0        | 1        |

The output equation can be obtained from inspection. As is the case with most sequence detectors, the output Z is 1 for only one combination of present state and input. Thus we get  $Z = X \bullet Y_2 \bullet Y_1' \bullet Y_0$ .

This can be simplified by noting that the state 111 does not occur, so the answer is  $Z = X \bullet Y_2 \bullet Y_0$ .

### Step 5 – <u>Separate the Transition Table into 3 Tables</u>, One for Each Flip-Flop

We shall generate a present state / next state table for each of the three flipflops; labeled  $Y_2$ ,  $Y_1$ , and  $Y_0$ . It is important to note that each of the tables must include the complete present state, labeled by the three bit vector  $Y_2Y_1Y_0$ .

| Y2          |                  |                     | Y1          |                  |                  | Y0          |          |       |

|-------------|------------------|---------------------|-------------|------------------|------------------|-------------|----------|-------|

| PS          | Next Sta         | ate                 | PS          | Next St          | ate              | PS          | Next Sta | ite   |

| $Y_2Y_1Y_0$ | $\mathbf{X} = 0$ | X = 1               | $Y_2Y_1Y_0$ | $\mathbf{X} = 0$ | X = 1            | $Y_2Y_1Y_0$ | X = 0    | X = 1 |

| 000         | 0                | 0                   | 000         | 0                | 0                | 000         | 0        | 1     |

| 001         | 0                | 0                   | 001         | 0                | 1                | 001         | 0        | 1     |

| 011         | 1                | 0                   | 011         | 0                | 1                | 011         | 0        | 1     |

| 100         | 0                | 1                   | 100         | 0                | 0                | 100         | 0        | 1     |

| 101         | 0                | 0                   | 101         | 0                | 1                | 101         | 0        | 1     |

| Match       | $\mathbf{Y}_1$   | $Y_2 \bullet Y_0$ ' |             | 0                | $\mathbf{Y}_{0}$ |             | 0        | 1     |

$$D_2 = X' \bullet Y_1 + X \bullet Y_2 \bullet Y_0'$$

$$D_1 = X \bullet Y_0$$

$$D_0 = X$$

Slide 16 of 23 slides Revised 9/28/2009 Copyright © 2009 by Edward L. Bosworth, Ph.D. All rights reserved.

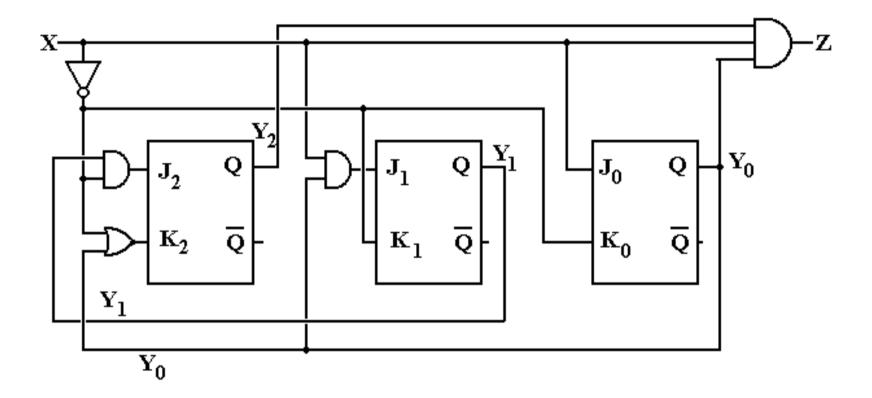

# Step 6 – <u>Decide on the type of flip-flops to be used</u>.

The problem stipulates JK flip-flops, so we use them.

| Q(T) | Q(T + 1) | J | K |

|------|----------|---|---|

| 0    | 0        | 0 | d |

| 0    | 1        | 1 | d |

| 1    | 0        | d | 1 |

| 1    | 1        | d | 0 |

Steps 7 and 8 are skipped in this lecture.

### Step 9 – <u>Summarize the Equations</u>

The purpose of this step is to place all of the equations into one location and facilitate grading by the instructor. Basically we already have all of the answers.

$Z = X \bullet Y_2 \bullet Y_0$   $J_2 = X' \bullet Y_1 \text{ and } K_2 = X' + Y_0$   $J_1 = X \bullet Y_0 \text{ and } K_1 = X'$  $J_0 = X \text{ and } K_0 = X'$

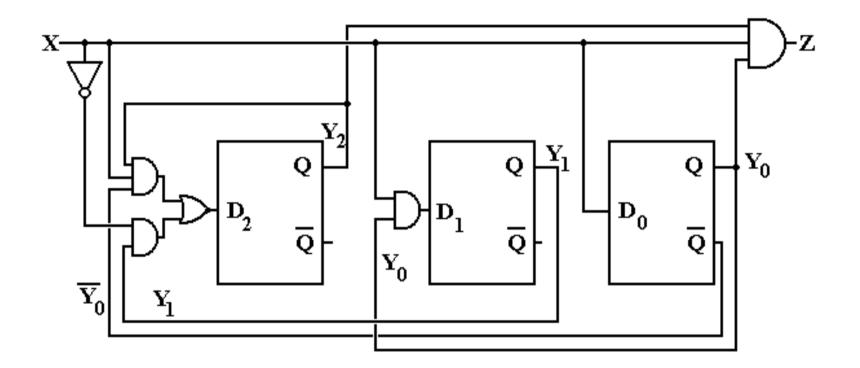

### Step 10 – <u>Draw the Circuit</u>

Here is the same design implemented with D flip-flops.

### More on Overlap – What it is and What it is not

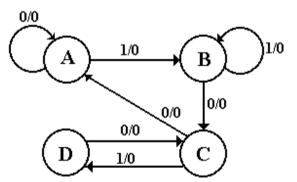

At this point, we need to focus more precisely on the idea of overlap in a sequence detector. For an extended example here, we shall use a 1011 sequence detector.

The next figure shows a partial state diagram for the sequence detector. The final transitions from state D are not specified; this is intentional.

1011 Sequence Detector Partial Design - Lacking Final Transition

Here we focus on state C and the X=0 transition coming out of state D. By definition of the system states,

State C – the last two bits were 10

State D – the last three bits were 101.

If the system is in state D and gets a 0 then the last four bits were 1010, not the desired sequence. If the last four bits were 1010, the last two were 10 - go to state C. The design must reuse as many bits as possible.

Note that this decision to go to state C when given a 0 is state D is **totally independent** of whether or not we are allowing overlap. The question of **overlap concerns what to do when the sequence is detected**, not what to do when we have input that breaks the sequence.

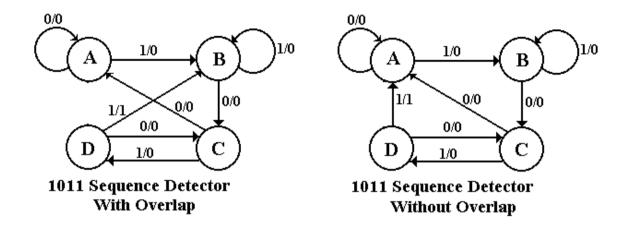

Just to be complete, we give the state diagrams for the two implementations of the sequence detector – one allowing overlap and one not allowing overlap.

The student should note that the decision on overlap does not affect designs for handling partial results – only what to do when the final 1 in the sequence 1011 is detected.